## Front-End Electronics Design and Construction

Jean-François Genat

SiLC 2<sup>d</sup> Workshop, LPNHE Paris

February 2d-3d 2006

Beam tests session

# Front-End Electronics Design

### Keep intrinsic detector performance

300 mm thick Silicon strip detector

Charge: 25000 e-/1000e- = 25

• Position \_\_\_\_ to a few  $\mu m$

Time:

BC Tagging

Position O(1) ns (Talk by Jacques David)

~ 1cm resolution //

# Noise and Power

| Noise | Source            | Value                    | Noise   |

|-------|-------------------|--------------------------|---------|

|       | Input stage       | g <sub>m</sub> =0.69mA/V | 1065 e- |

|       | Detector leak     | 10 nA                    | 588 e-  |

|       | Biasing resistors | 10 MΩ                    | 423 e-  |

|       | Total             |                          | 1288 e- |

Foreseen detector noise contributions at 30 pF detector capacitance and 3  $\mu s$  shaping time in 130nm CMOS technology

#### Power

- Preamp + Shaper + Sparsifier

| <b>Preamp: 70</b> μ <b>W</b> | <b>Shaper: 160</b> μ <b>W</b> | Sparsifier: 50 μW           |

|------------------------------|-------------------------------|-----------------------------|

| Sampling:                    |                               | <b>100 - 200</b> μ <b>W</b> |

- ADC

**ADC:** 110 μW

Total:500 - 600 mW/channelPower cycling : save 99%

# Front-End Electronics Design

Guidelines

As compact as possible:

- Tr anspar ency

- Less passive parasitics: better S/N

- In principle simpler...

## Patrick Le Du (Saclay): Summary of current thinking

{ The ILC environment poses new challenges & opport unities which will need new technical advances in Data Collection

### $\rightarrow$ NOT LEP/SLD, NOT LHC !

#### The FEE integrates everything

→ From signal processing & digitizer to the RO BUFFER ...

- Very large number of channels to manage (Trakers & ECal)

- Interface and feedback between detector and machine is fundamental →optimize the luminosity → consequence on the DAQ architecture

- Classical boundaries are moving : Slow control, On/ Off line ... }

# Front-End Electronics Components

### Front - end Analog:

- Integrate 512-1024 channels in 130nm CMOS:

amplifiers

shapers two time scales wrt strip length

samplers 8 samples over two peaking times

ADC

Power switching

- Presently measured in 180nm CMOS

| amplifiers: | 500 + 16 e-/ pF   |

|-------------|-------------------|

| shapers:    | 375 + 10.5 e-/ pF |

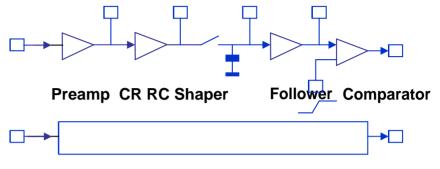

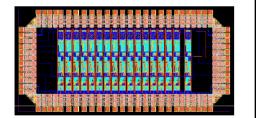

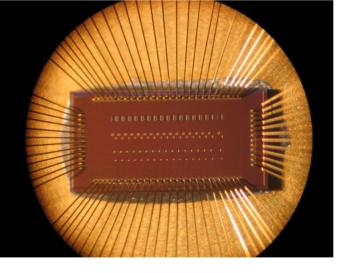

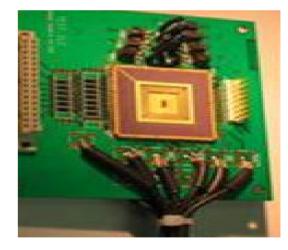

## Paris Front-end 1st Prototype Chip

(Thanh Hung Pham's talk)

- Low noise amplification + pulse shaping

- Pulse sampling

- Threshold detection

- Power dissipation less than 500  $\mu$ W/c

#### Technology: CMOS 180 nm

16 identical channels

#### Successfully checked.

3mm

#### Next design in progress CMOS 130 nm

# Front-End Electronics Components

### Front - End Digital

- Buffer memory

- Processing for

- Calibrations

- Amplitude and time least squares estimation, centroids ?

- or/and Raw data after zero suppression lossless compression

#### Tools

- Digit al libraries in 130nm CMOS available

- Synt hesis f r om VHDL/ Verilog

- SRAM memory

- PLLs

## Front-End Electronics

#### Passive

Capacit or s: Large values: Decouplings

### • Cables:

Signals:Fiber opticsPower:Copper

# Grounding & Shielding

Signal is refered to the backplane

AC stick preamp ground and DC supplies to this voltage using (large) decoupling capacitors

Shield all det ect or f r om ext er nal int er f er ences using a t hin aluminum foil wrapped around the cqrbon fiber support structure

Digital I/Os

Use fiber optics:

- Trains stage: 3-6 MHz BCO synchronous controls

- Digitization stage: 100 MHz ADC clock

- Transfer stage: >1 GHz fiber serial clock

# Detector coupling

### DC coupling

Cheaper detector process but:

DC current flowing through preamp may induce pedestals reduce dynamic range, saturations

OK using synchronous reset and sampling

AC coupling

Needs an on-detector oxide layer

No preamp reset needed, but 1/f noise to be removed OK with sampling

Caveat: oxide pin-holes may short detector to FE chip

Conclusion: The present front-end electronics can manage both solutions, so go to the safest and cheapest !

Courtesy: Marty Breidenbach (Cal SiD)

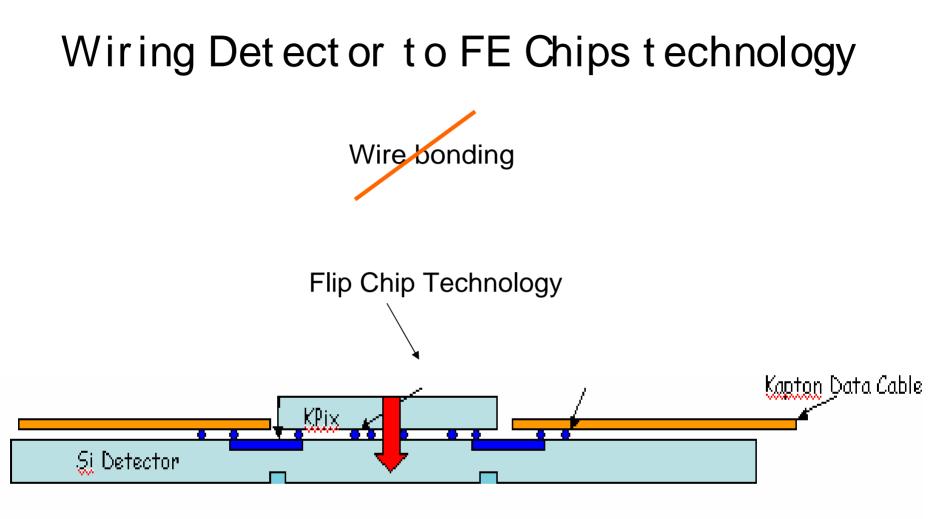

## Manuel Lozano (CNM Barcelona) Chip connection

- Wire bonding

- Only periphery of chip available for IO connections

- Mechanical bonding of one pin at a time (sequential)

- Cooling from back of chip

- High inductance (~1nH)

- Mechanical breakage risk (i.e. CMS, CDF)

- Flip-chip

- Whole chip area available for IO connections

- Automatic alignment

- One step process (parallel)

- Cooling via balls (front) and back if required

- Thermal matching bet ween chip and substrate required

- Low induct ance (~0.1nH)

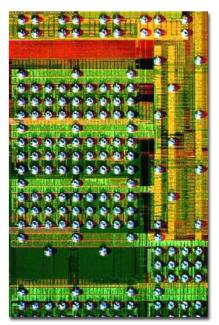

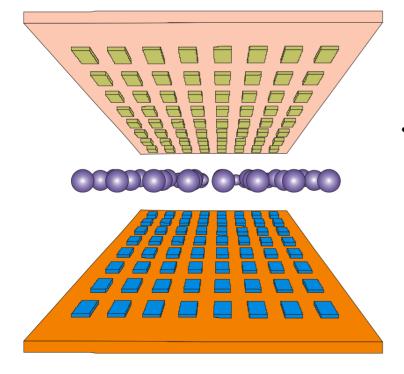

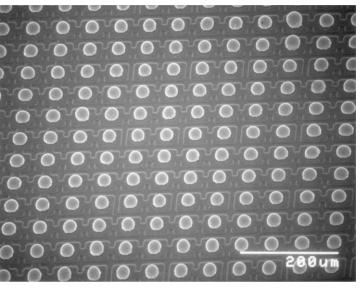

## *Manuel Lozano (CNM Barcelona)* Bump bonding flip chip technology

Electrical connection of chip to substrate or chip to chip face to face

### flip chip

Use of small metal bumps

### bump bonding

CNM

- Process steps:

- Pad metal conditioning:

Under Bump Metallisation (UBM)

- Bump growing in one or two of the elements

- Flip chip and alignment

- Reflow

- Optionally underfilling

## Manuel Lozano (CNM Barcelona) Bump bonding flip chip technology

- Expensive technology

- Especially for small quantities (as in HEP)

- Big over head of NRE cost s

- Minimal pitch reported: 18 µm but ...

- Few commercial companies for fine pitch applications (< 75 μm)</li>

- Bumping technologies

- Evaporation through metallic mask

- Evaporation with thick photoresist

- Screen printing

- Stud bumping (SBB)

- Electroplating

- Electroless plating

- Conductive Polymer Bumps

- Indium evaporation

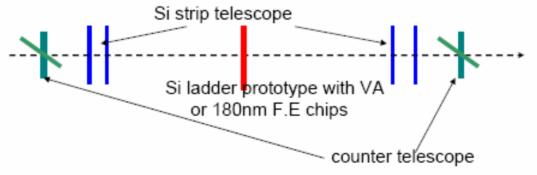

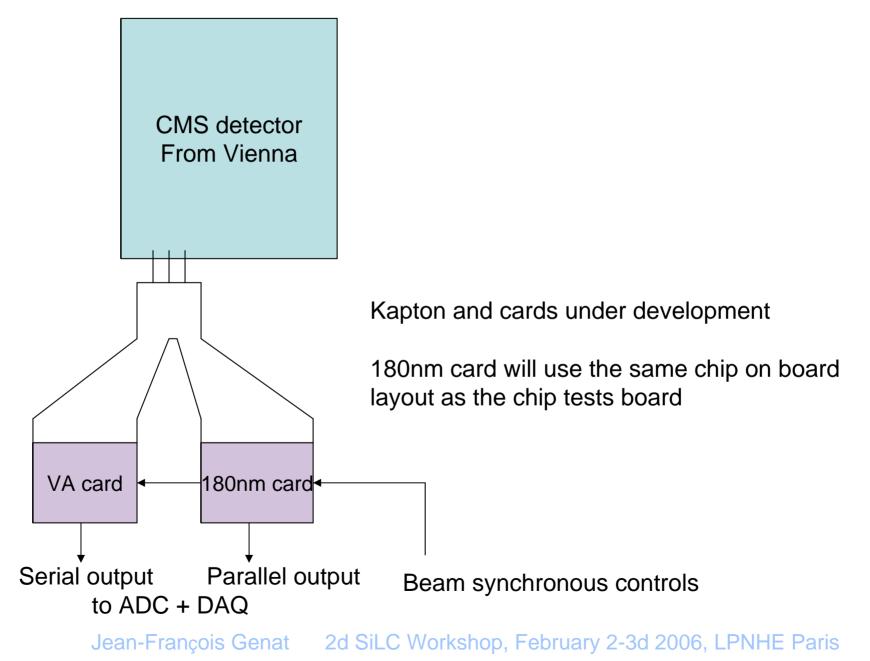

# Beam-tests

```

At 5 Gev e- beam in DESY, no B

```

Very simple telescope set-up in Silicon strips (2 ladders of CMS strips, one read out with VA1 FE and the other one with a few channels read out with present version of new FE chip), together with a reference telescope;

Purposes:

To check S/N for the long strip first proto measured at Lab test bench To characterize performances of the new FE chip in realistic conditions after doing it at Lab test bench and comparing with ref FE electronics (VA1)

# Tests Hardware

# Tests Software

### **Standard VME ?**

PC + USB ?

This document was created with Win2PDF available at <a href="http://www.win2pdf.com">http://www.win2pdf.com</a>. The unregistered version of Win2PDF is for evaluation or non-commercial use only.