# Front-end Chip: From CMOS 180nm to 130nm

- Introduction

- Circuit in 180nm technologies

- Challenges in 130nm technologies

- Circuit architecture

- Perspective

## Introduction

Encouraging result from front-end in 180nm CMOS

→ Design the new front-end chip in 130nm process

$\rightarrow$  Less on- Si detector material, less parasitics, less power

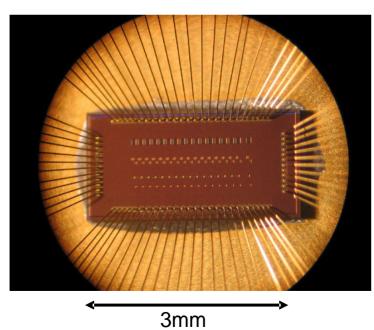

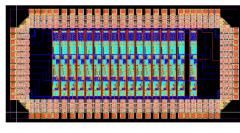

#### Front-end Prototype chip in 180nm technologie

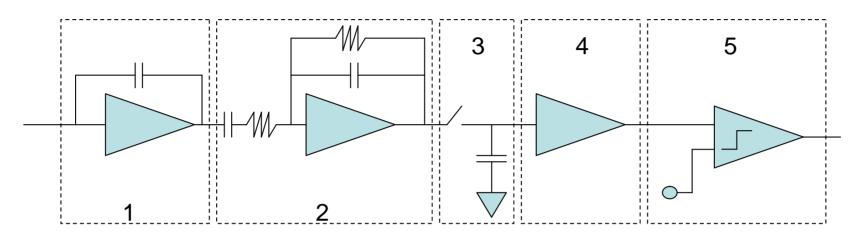

17 channels (one test Channel)

- 1. Low noise amplification

- 2. Pulse shaper

- 3. Sample and Hold

- 4. Buffer

- 5. Comparator

### Results in 180nm

#### **Preamp Results**

| Gain:                                                                                      | 8mV/MIP    |                |              | OK |

|--------------------------------------------------------------------------------------------|------------|----------------|--------------|----|

| Oynamic range:                                                                             | 50 MIP     |                |              | OK |

| Linearity:                                                                                 | +/-1.5%    | expected: +/-( | ).5%         | -  |

| Noise @ 70 μW power, 3μs-20μs rise-fall times:                                             |            |                |              |    |

| 498 +                                                                                      | 16.5 e-/pF | 490 + 16.5 e-  | /pF expected | OK |

| Pulse Shaper results                                                                       |            |                |              |    |

| Peaking time: 2-6 $\mu$ s tunable peaking time vs 1-10 expected                            |            |                |              | -  |

| Linearity: 6%, 3.5% expected                                                               |            |                |              | -  |

| Noise @ 3 μs shaping time and 70 μW power:<br>325 + 10.1 e-/pF vs 274 + 8.9 e-/pF expected |            |                |              | OK |

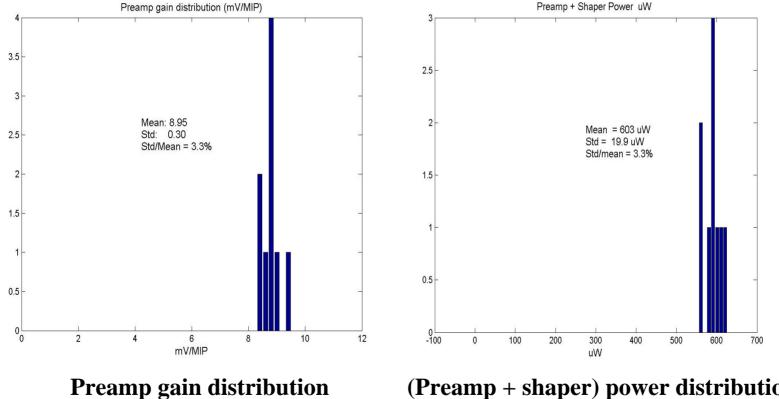

#### Results in 180nm

Process spreads: 3.3% •

(Preamp + shaper) power distribution

#### Front-end in 130nm

Cooperation between LPNHE and LAPP Annecy

Why 130nm ?

VLSI Will be dominant in industry in the next few years Faster Low power

But, it is also more difficult for low noise analog design

#### **Technologies** parameters

- 180 nm Mixed-mode process (including 3.3V transistors)

- 6 metals layers

- Cox = 0.0049 F/m<sup>2</sup> (Low voltage 3.3V transistor)

- Gate's minimum width= 0.5μm

- Metal/Metal capacitance =  $1 fF/\mu m^2$

- Various Vt options

- 130nm Mixed-mode process (including 3V3 transistors)

- 8 metals layers

- Cox = 0.0048 F/m<sup>2</sup> (Low voltage 3.3V transistor)

- Gate's width minimum = 0.34µm

- Metal/Metal capacitance =1fF/um<sup>2</sup>

- Same Vt options

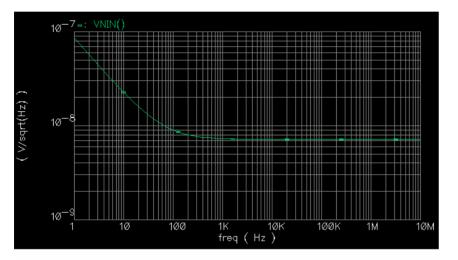

### Noise: 130nm vs 180nm (simulation)

• PMOS:

130nm W/L = 2m/0.5u Ids = 38.79u,Vgs=-190mV,Vds=-600mV gm=815.245u,gms=354.118u,gds=4.44907u <u>1MHz → 7.16nV/sqrt(Hz)</u>

Thermal noise hand calculation = 3.68nV/sqrt(Hz)

180nm W/L=2m/0.5u Ids=38.28uA,Vgs=-337mV,Vds=-0.6V gm=944.4uS,gms=203.1uS,gds=10.2uS <u>1MHz --> 3.508nV/sqrt(Hz)</u> Thermal noise hand calculation = 3.42nV/sqrt(Hz)

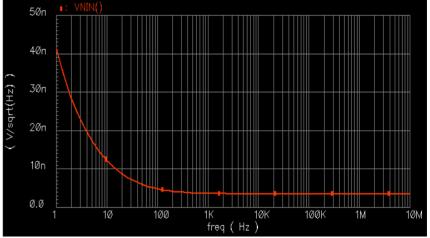

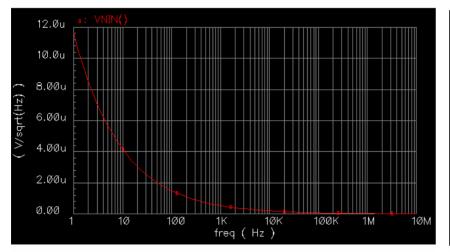

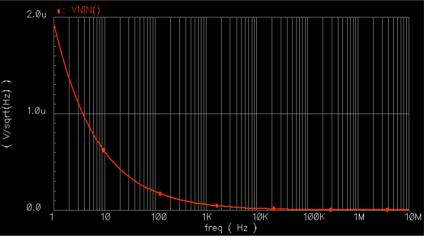

### Noise: 130nm vs 180nm (simulation)

#### • NMOS :

130nm W/L = 50u/0.5u Ids=48.0505u,Vgs=260mV,Vds=1.2V gm=772.031uS,gms=245.341uS,gds=6.3575uS **1MHz --> 24.65nV/sqrt(Hz)**

100MHz --> 5nV/sqrt(Hz) Thermal noise hand calculation = 3.78nV/sqrt(Hz)

180nm W/L=50u/0.5u Ids=47uA,Vgs=300mV,Vds=1.2V gm=842.8uS,gms=141.2uS,gds=16.05uS <u>1MHz --> 4nV/sqrt(Hz)</u>

10MHz --> 3.49nV/sqrt(Hz) Thermal noise hand calculation = 3.62nV/sqrt(Hz)

## Perspective

- The noise problem is under investigation

- If a solution is found, the chip is expected to be submitted mid-April

- Otherwise, goto:

- CMOS IBM (less noise according to people from NIKHEF and Pavia) or

- SiGe (1/f far better, thermal OK)

This document was created with Win2PDF available at <a href="http://www.win2pdf.com">http://www.win2pdf.com</a>. The unregistered version of Win2PDF is for evaluation or non-commercial use only.